The FC118 FPGA IP core provides a high-resolution complex Fast Fourier Transform (FFT) function in a resource-efficient high-speed streaming implementation. This highly-customizable core is ideally suited for channellizing applications such as Software Defined Radio, SDR, and sophisticated audio processing. Compared to a conventional FFT of the same length, the FC118’s Polyphase prefilter provides greatly improved channel selectivity with minimal additional resources. This core is available both in source and netlist form for Virtex-II Pro, Virtex-4 and Virtex-5.

Features

Items marked with * are selectable when the order is placed.

- Number of frequency bins is run-time programmable in powers of 2, up to a limit determined when the module is ordered*, maximum 65,536 points

- Complex inputs and outputs

- Two parallel channels per module with shared prefilter coefficients

- Natural order for both input and output, or natural-in bit-reversed out

- Continuous streaming: one datum in & out per clock cycle

- Clock enable input in cases where input data is not available on every cycle

- Forward / Inverse transform selectable at runtime

- 8- to 24-bit* signed input and output, binary point may be in any position

- to 24-bit* FFT coefficients

- Adjustable scaling factors for each Radix-4 stage (one final Radix-2 stage used if number of bins is not an even power of 2), or block floating-point, or unscaled arithmetic*

- FFT operations use convergent rounding or truncation*

- Cores may target Xilinx parts including Virtex2-Pro, Virtex-4, and Virtex-5

- Prefilter size is a selectable multiple of the FFT size*

- Overflow indicators for both the prefilter and FFT blocks

- Available stand-alone or packaged for use with 3L Diamond/FPGA

- Resource vs. speed trade-offs available to meet application requirements*.

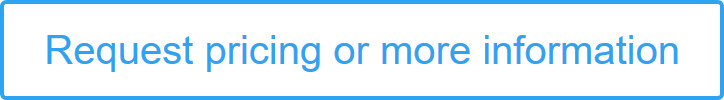

I/O interfaces for stand-alone version with 16-bit input, output and coefficient widths:

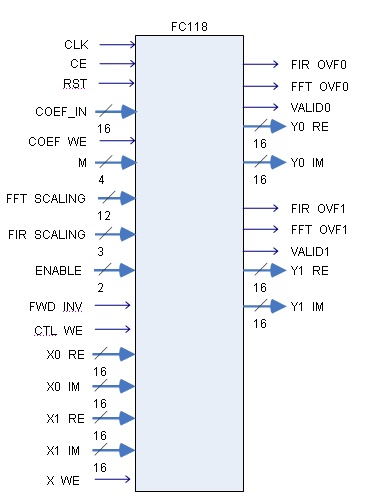

I/O interfaces for 3L Diamond/FPGA version:

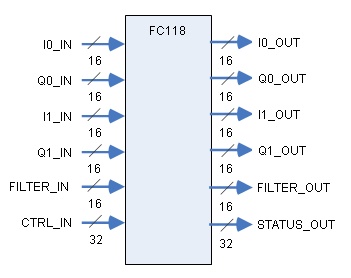

Example resource usage and timing results for dual-channel 2k-point, 16 bit, scaled version with 8x prefilter (provides selectivity performance up to that of a 16k-point conventional FFT):

FC118 is a complete module that includes:

- Netlist file, or VHDL source code available for additional charge

- 3L Diamond/FPGA integration support (.fcd, _pkg.vhd files) and example implementations

- VHDL testbench (requires Active-HDL or equivalent simulation environment)

- User’s Guide

- C Simulation Model (available on request)

- MATLAB Simulation Model and PARS model under Simulink (available on request)