FPGA-Based Spur Suppression in the FMC-ADC500CD

Introduction

In high-speed digital signal acquisition systems, one of the most pressing challenges is increasing the sampling rate without compromising signal integrity. A widely used method to achieve this goal is ADC interleaving, which combines multiple ADC cores operating in parallel to emulate a higher effective sampling rate. However, while this technique boosts data throughput, it also introduces artifacts — particularly spurious signals (spurs) — due to mismatches between the individual ADCs.

This article explores how ADC interleaving works, the typical sources of spurious signals, and how these spurs degrade system performance. We then highlight how the FMC-ADC500CD from Sundance DSP, based on the ADS54J60 from Texas Instruments, uses advanced FPGA firmware to eliminate interleaving spurs, delivering a clean and reliable high-speed digitization platform.

What Is ADC Interleaving?

Principle of Operation

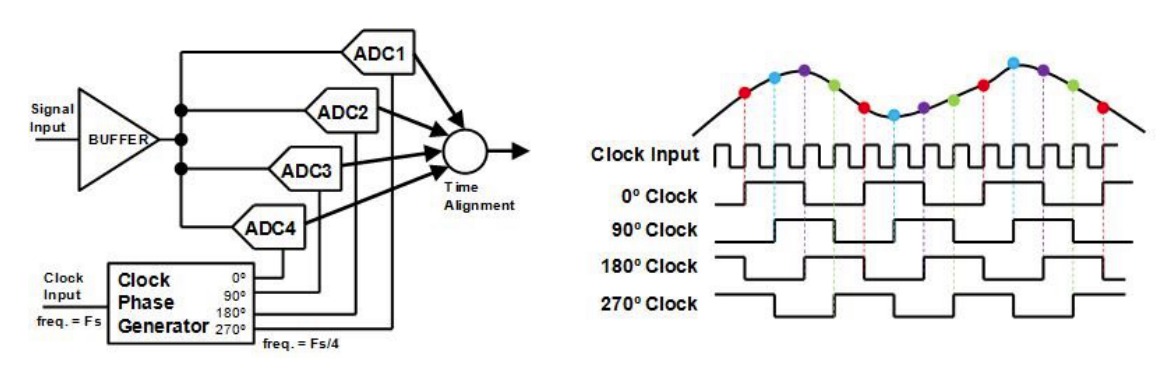

ADC interleaving increases the effective sampling rate by using multiple ADCs in parallel, each sampling the input signal at staggered time intervals. For example, if four ADCs are interleaved and each operates at 250 MSPS, the combined system achieves an effective 1 GSPS sampling rate.

This technique allows designers to overcome clocking and power limitations of single high-speed ADCs by distributing the work across multiple lower-speed cores.

The Problem: Interleaving Spurs

Despite its benefits, interleaving introduces periodic errors if the individual ADC cores are not perfectly matched. These mismatches manifest in the frequency domain as spurious tones, commonly referred to as interleaving spurs.

Main Sources of Spurs

-

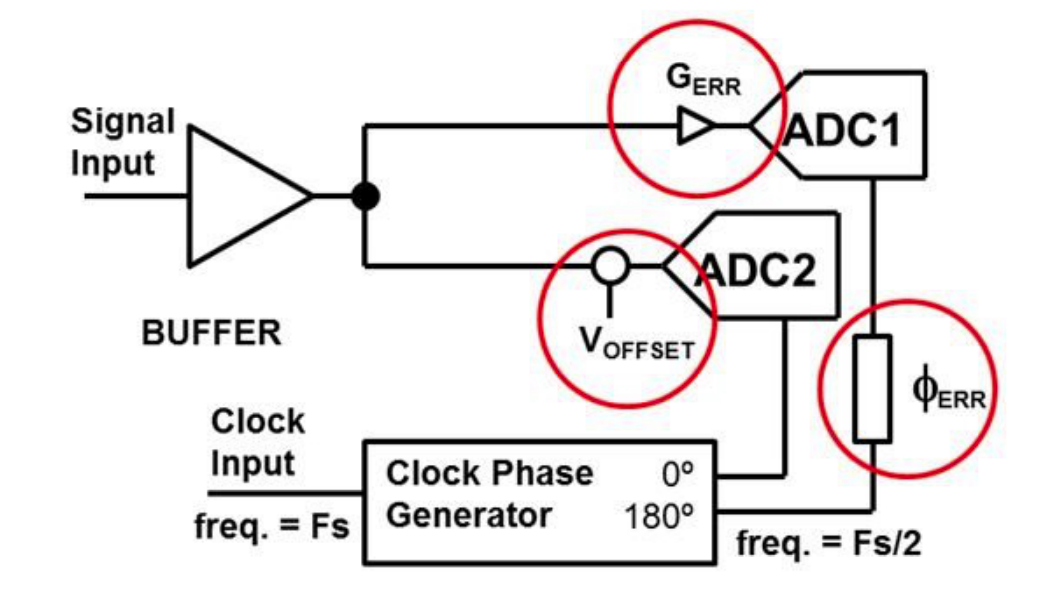

Gain Mismatch

If ADC cores have slightly different gains, the resulting amplitude variations cause periodic modulation.

Effect: Spurs at multiples of the interleaving frequency (e.g., Fs/N, 2Fs/N, etc.). -

DC Offset Mismatch

If each ADC has a different zero-point voltage, the composite output shows a repeating offset pattern.

Effect: Spurs near DC and at interleaving harmonics. -

Timing Skew (Phase Error)

Timing mismatch between ADC sample clocks causes phase distortion, especially problematic at higher input frequencies.

Effect: Spurs and non-linear distortion increase with signal frequency.

These spurs degrade SNR, reduce ENOB, and can mask or distort real signal components — making interleaving unusable without effective correction.

The ADS54J60 and Interleaving in the FMC-ADC500CD

The FMC-ADC500CD from Sundance DSP is a high-performance FMC module designed for RF, instrumentation, and defense applications. At its core is the Texas Instruments ADS54J60, a dual-channel, 16-bit ADC that supports sampling rates up to 1 GSPS per channel.

To reach this speed, the ADS54J60 internally uses four interleaved ADC cores, each running at 250 MSPS. This internal interleaving is transparent to the user, but it does introduce the same interleaving spurs discussed earlier. Without correction, these spurs can significantly impact the accuracy and fidelity of captured data.

Our Solution: FPGA Firmware for Spur Elimination

To address this issue, Sundance DSP has developed a custom FPGA calibration engine implemented directly on the FMC-ADC500CD firmware. This firmware performs real-time correction of all interleaving artifacts, completely removing spurious components from the signal.

Key Capabilities of the FPGA Calibration Engine

-

Gain Calibration:

Dynamically equalizes the gain of each ADC core to eliminate amplitude-related spurs. -

DC Offset Compensation:

Measures and subtracts per-channel bias voltages from the output stream. -

Timing Skew Correction:

Performs phase alignment using high-precision digital interpolation to ensure correct temporal sampling.

Unlike static calibration tables, our FPGA-based system can operate continuously to adapt to temperature drift, voltage fluctuations, and component aging, ensuring long-term accuracy.

Before and After: Spurs Removed

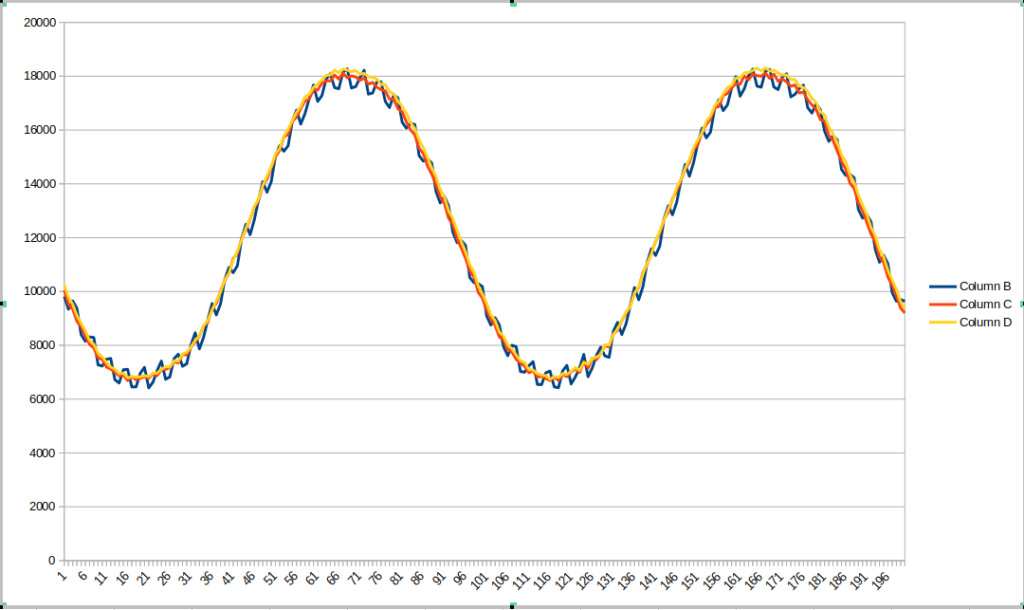

In this graph, Channel B represents the output from an uncalibrated ADC core, while Channels C and D show the results after applying Sundance DSP’s FPGA-based calibration.

All three channels exhibit periodic waveforms, but a closer inspection reveals a critical difference: Channel B contains visible spurious noise components, artifacts introduced by interleaving mismatches such as gain variation, DC offset, and timing skew.

These spurs manifest as irregularities superimposed on the signal, degrading its spectral purity and potentially masking real signal content. In contrast, Channels C and D demonstrate the effectiveness of our calibration engine. The spurious tones are either completely eliminated or significantly attenuated, resulting in cleaner and more consistent signal traces.

This visual comparison underscores the importance of dynamic, FPGA-based spur suppression, especially in mission-critical applications like radar, sonar, ADAS, and medical imaging, where signal fidelity directly impacts system performance and reliability.

Conclusion

ADC interleaving is an essential technique for achieving gigasample-per-second performance, but it introduces spurs that can cripple system performance if left uncorrected. The ADS54J60 used in the FMC-ADC500CD utilizes internal 4x interleaving to achieve 1 GSPS sampling, and Sundance DSP’s FPGA-based spur elimination firmware ensures that this performance comes without the cost of signal artifacts.

By accurately correcting gain, offset, and timing mismatches, our solution delivers clean, reliable, and high-resolution data, making the FMC-ADC500CD ideal for mission-critical applications in radar, wireless communication, electronic warfare, and test instrumentation.