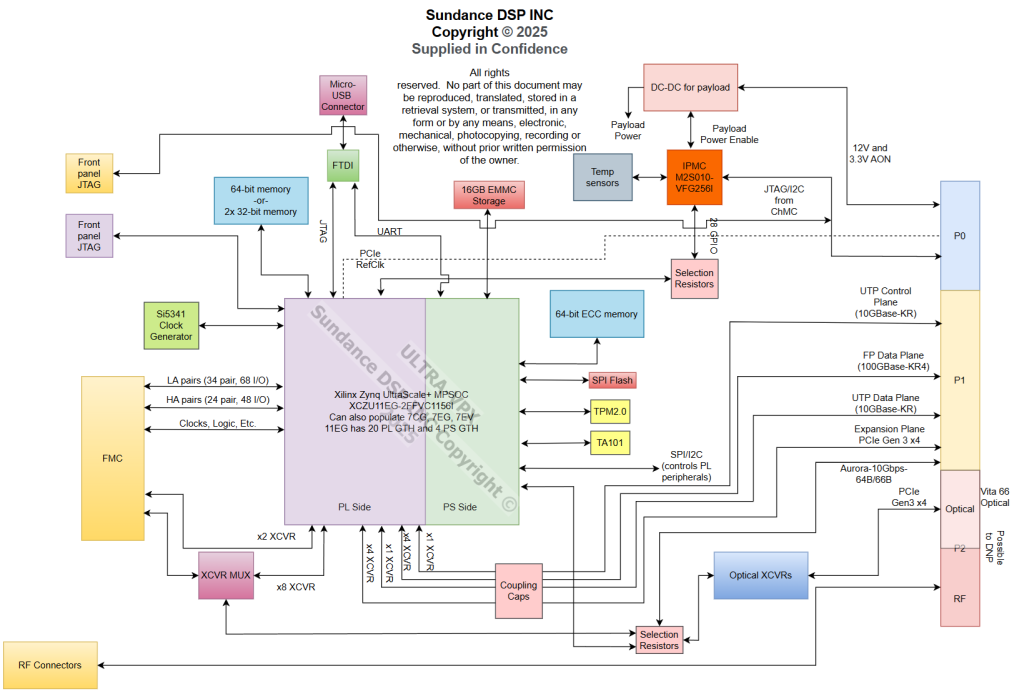

The SE1000, Ultra-VPX , is a 3U payload device featuring a AMD Zynq MPSoC device in the FFVC1156 Package. The standard device used is the XCZU11EG-2FFVC1156I but can be populated with 7EV, 7EG, or 7CG devices in either extended or Industrial temperature grades (MOQ may apply). The board is suitable for high-speed data acquisition, processing, and analysis as well as command/control. The board is designed for defense, aerospace, and research applications.

Features

- Board form factor: SOSA slot profile SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11- 1

- IPMC: Microchip SmartFusion2 SoC (M2S010-VFG256I)

- Main payload device: Xilinx Zynq MPSoC XCZU11EG-2FFVC1156I with the possibility to populate Xilinx Zynq MPSoC 7EV, 7EG, or 7CG

- PL memory: 64-bit or 2 banks 32-bit wide TBD GB capacity

- PS memory: 64-bit with 8-bit ECC or 72-bit wide TBD GB capacity

- 16 GB eMMC for PS image and data storage (can populate up to 256GB)

- 1GB QSPI flash for PS image and data storage

- TA101 Secure authentication IC connected to PS for secure boot and encryption capabilities

- 0 for storage of encryption keys for the PS

- Si5341 Clocking IC, 10 output, low jitter, configurable clocking IC provides fabric clocks and transceiver clocks

- FT4232 USB to UART: Provides 3 UART channels (one for the payload PS, one for payload PL, and one for the IPMC) both accessible via a front panel Micro-USB connector

- Separate JTAG headers for the payload and IPMC, both front panel accessible

- FMC Connector with 34 LA bank pairs, 24 HA bank pairs, and full clock, and logic routing

- FMC Connector can have 10 XCVRs routed to it depending on XCVR Mux option, otherwise, it will have two XCVRs routed to it be default with the appropriate XCVR reference clocks

- Using selection resistors it is possible to route 4 PS XCVRs to the P2A optical aperture to realize a Gen 2 x4 lanes PCIe interface or to route 4 PL XCVRs to realize a Gen 3 x4 lanes PCIe interface

- On the P1 connector PL transceivers will be routed to the UTP Control Plane (10GBase-KR) (x1 XCVR), FP Data Plane (100GBase-KR4) (x4 XCVR), UTP Data Plane (10GBase-KR) (x1 XCVR), Expansion Plane PCIe Gen 3 x4 (x4 XCVR), and the Aurora-10Gbps-64B/66B (x4 XCVR)

- If space exists, there will be front panel accessible JTAG connectors for the payload and IPMC respectively

- If space exists, there will be front panel accessible RF connectors that directly connect to the RF pins on the backplane (The P2B connector is optional to populate).

- Shunt resistors on GPIO lines between the IPMC and the Payload can be removed depending on the assembly option

- Voltage and current sensing ICs connected to IPMC GPIO

- Temperature Sensing IC connected to the IPMC GPIO

- Onboard DC-DC converters that have the capability of being enabled and disabled via the IPMC, the DC-DC converters supply various voltage planes responsible for powering the ICs, Payload, and different voltage domains required by the Payload

- From the chassis the board requires both the 12V supply and the 3.3V AUX supplies

Enclosure will be able to comply with Vita 48.2 conduction cooling requirements and Vita 48.8 air cooling requirements

Applications

- Defense

- Medical

- Imaging

- Industrial automation

- Software Defined Radio

A complete BSP with Linux driver will be supplied.

Early access to this board can be granted to interested customers but the estimated delivery for prototype version will be Q2 of 2026.

SE1000-xxxxxxx-yy where “xxxxxxx” can be any of the options in Table 1: AMD Payload Options and “yy” can be any of the -n P2 connectors options shown in the Table 2: P2 Connector Options below

Table 8: AMD Payload Device Options

| AMD Device option | Description |

| ZCU11EG | AMD Zynq Ultrascale+ 11EG in the FFVC1156 ball package, 4 PS GTR, 20 PL GTR, Quad ARM A53, Dual ARM R5F |

| ZCU7EV | AMD Zynq Ultrascale+ 7EV in the FFVC1156 ball package, 4 PS GTR, 20 PL GTR, Quad ARM A53, Dual ARM R5F, integrated VCU |

| ZCU7EG | AMD Zynq Ultrascale+ 7EG in the FFVC1156 ball package, 4 PS GTR, 20 PL GTR, Quad ARM A53, Dual ARM R5F |

| ZCU7CG | AMD Zynq Ultrascale+ 7CG in the FFVC1156 ball package, 4 PS GTR, 20 PL GTR, Dual ARM A53, Dual ARM R5F |

| -TBD | Other options may be supported. Please contact Sundance DSP support for more information |

Table 9: P2 Connector Options

| “-n” option | Description |

| -0 | No P2 connector installed |

| -6 | 2 Style C and 10 NanoRF |

| -12 | 2 Style C and 20 NanoRF |

| -14 | 2 Style D |

| -TBD | Other options may be supported. Please contact Sundance DSP support for more information |

Additional speed grades and temperature grades are available; payload device will be -2 speed grade and -I Industrial temperature grade by default.

Default part number is:

SE1000-XCZU11EG-0 AMD Zynq Ultrascale+ 11EG in the FFVC1156 ball package, PL memory 64-bit 8 GB, PS memory 8 GB, 16 GB eMMC, 1GB QSPI flash