OVERVIEW:

• Mil-Std-1553 Intellectual Property for FPGAs and ASIC

• Suitable for any MIL-STD-1553 BC, RT, MT implementation

• Local Bus or Axi interface

• Small FPGA area utilization

• Modular architecture allowing flexible implementations

• Provided with verification environment

• Based on vendor and technology independent VHDL code

• Configurations available: Simple Front-End, Local Bus and Axi interface

HIGHLIGHTS:

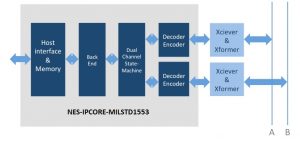

Combining the benefits of programmable devices (FPGA) and our Embedded systems IP Cores provides a small-size, robust, reliable, flexible, future-proof and cost effective solution for Mil-Std-1553 interface. Our Embedded systems IP cores are designed for any requirement and application. Customers can choose between various configurations and interfaces. From the very small and simple 1553 Front-End (FE), designed for simple applications, where no CPU is controlling the system, to the most complex implementations, where a Local Bus is used by the CPU (D) or Axi bus. The FC-1553 is available and is working with any FPGA, clock frequency and 1553 transceiver, providing the most robust, yet flexible, solution.

OVERVIEW

• Mil-Std-1553 Intellectual Property for FPGAs and ASIC

• Suitable for any MIL-STD-1553 BC, RT, MT implementation

• Local Bus or Axi interface

• Small FPGA area utilization

• Modular architecture allowing flexible implementations

• Provided with verification environment

• Based on vendor and technology independent VHDL code

• Configurations available: Simple Front-End, Local Bus and Axi interface

COMPATIBILITY

MIL-STD-1553, MIL-STD-1553B Notice 2 and 1760, RT Validated according to test plan from MIL-HDBK-1553A, 1Mbps Data Rate.

Connects to any transceiver transformer pair

FC-1553 RAM

4, 8, 16, 32, 64K by 16 bits Dual Port

RAM (Limited by FPGA resources only)

CLOCK

Any even frequency from 12MHz and higher (12, 14, 16… 98, 100MHz, …)

Including 33MHz for PCI and 125MHz for PCI Express implementations

SUPPORTED FPGAs

Any FPGA with sufficient number of LUTs and Dual-Port memory

FPGA families from the following vendors: Xilinx, Altera, Lattice, Actel

BACKEND INTERFACE

Local Bus or PCI, compatible with existing drivers and applications.

No need to rewrite drivers’ code

Eliminates replacement risk

MANCHESTER DECODER

The unique Manchester decoder can work with any clock reduce clock sources and clock domains on board (reduces EMI/RFI). Advanced algorithms for filtering out noise and disturbances enable the core to operate in harsh environments.

ADVANCED VERIFICATION

To ensure a fully reliable and robust product the core was developed using an advanced verification environment that includes a Random-Generation engine, Code Coverage and assertion tools. All 1553 protocol, functions and performance requirements were verified.

SIMPLE INTEGRATION

In order to simplify the integration of the core, a sample VHDL design that uses the core is provided, including a comprehensive user’s manual.

A VHDL gate level model of the core for the target technology.

A Transceiver VHDL model that connects the core with 2 buses.

A bus tester VHDL model that generates1553 messages and checks the return replies.

A top Test bench that instantiates all of these components to a working example.

A simulation script for compiling and running the core

| IP CORE | SUPPORTED CONFIGURATIONS | FPGA Memory Required | Clock Frequency | Approx Area Utilization LUT |

| FC-1553FE | BC/RT/MT | NO | 12MHz and up (*) | 1000(**) |

| FC-1553 | BC/RT/+MT | YES | 12MHz and up (*) | 4500(**) |

(*) Clock Frequency can be any even number of 12MHz or more (12, 14, 16MHz…). Maximum clock frequency depends on FPGA and the actual place & route.

(**) These numbers are approximate. Actual area usage may vary according to core configuration and FPGA

Cores for Any Mil-Std-1553 Implementation

FC-1553FE IP Core is the simplest solution for most applications, The FC-1553FE is suitable for simple 1553 applications, protocol translators and hardware based implementations.

FC-1553 is suitable for more complex 1553 implementations, where the application is controlled by software.