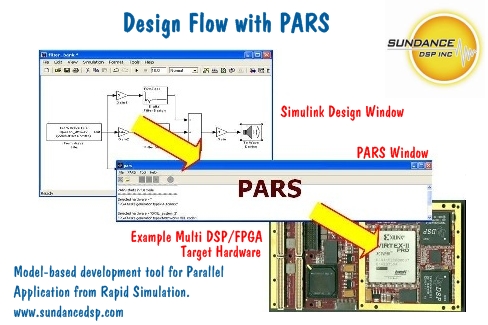

Parallel Application from Rapid Simulation (PARS) is a toolbox for ‘The MathWorks’ MATLAB® and Simulink®. This enabling technology allows a user to design an entire system within the MATLAB and Simulink environment and then automatically generate code for multi-DSP and multi-FPGA in the system, without writing a single line of C or VHDL code. All the inter-processor communication and synchronization code is built into the single application file. The generated application code will also contain all of the booting information for the entire multi DSP/FPGA platform. This advanced, but easy to use, tool also provides Hardware-In-the-Loop (HIL) capability to test the application on the hardware in real time.

PARS is a new and emerging technology for generating parallel applications that target hardware systems comprising multiple DSP and FPGAs from a single Simulink model. There are many software packages in the market that target a single DSP or FPGA from a Simulink model but so far none of them supports multiple DSPs and FPGAs and could generate a single application image.

PARS accepts a Simulink model as input, and helps users to partition the Simulink model into several tasks which will be placed on different DSPs, General purpose processors and/or FPGAs. PARS helps users calculate the size and type of all data transfers between different tasks and then generates the C source code with all necessary inter-task/inter-processor communication functions.

PARS checks the Simulink model for the presence of any possible deadlock and in case it finds any deadlock in the model, PARS tries to resolve them. In cases where the deadlock could not be resolved automatically, it will report the source of deadlock and guides the user to resolve it manually.

PARS hides the complexity of any parallel application development from the user and lets the user to only focus on algorithm development. User does not need to have deep understanding of parallel processing techniques or even DSP and FPGA. All developments are model based. By using PARS, even novices could generate a parallel deployable application from a single Simulink model in less than a few hours. This work was originally accomplished under a US Navy contract and Sundance DSP would like to acknowledge this support.

PARS training videos are available from here.