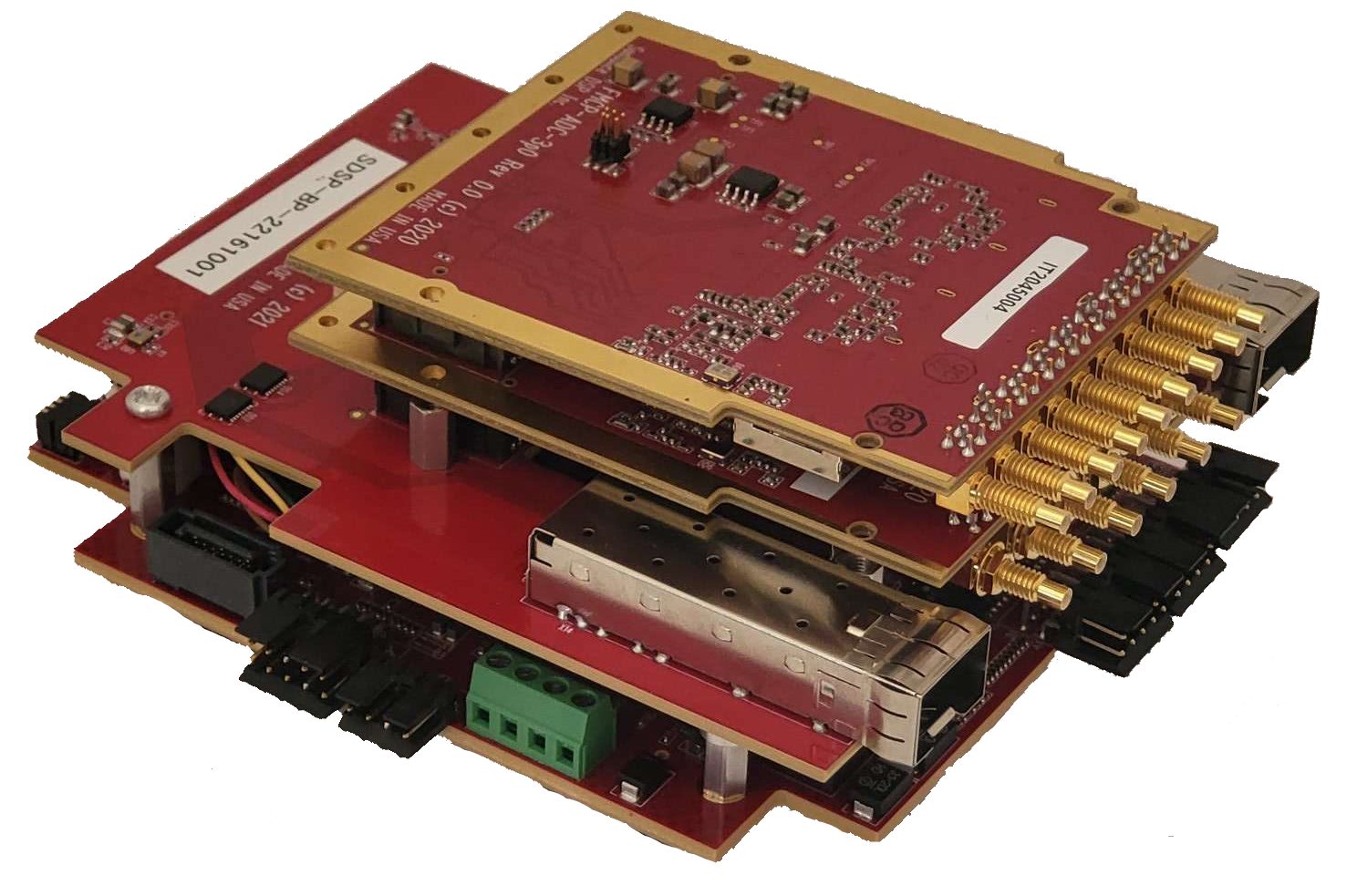

DL100 Data Logging Solution

- 4 channels of ADC at 3GS/s 14 bits

- 4 channels of DAC at 12GS/s 16 bits

- AMD Zynq US+ with 11EG-2 device

- optional custom enclosure

- includes complete BSP capable of logging all 4 channels of ADC data to attached SATA hard disk or suitable PCIe104 storage card

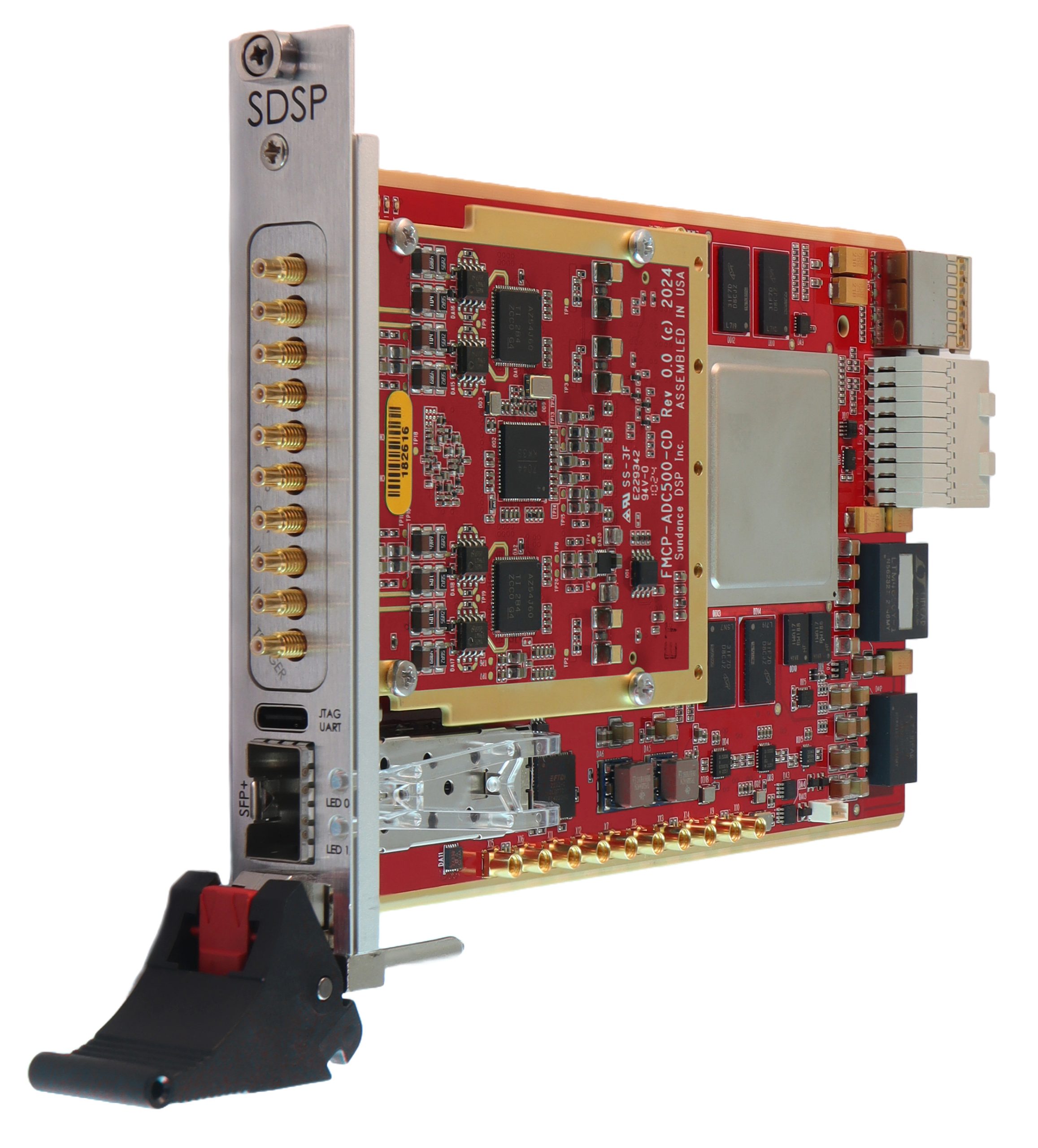

DL200 Data Logging Solution

- 4 channels of ADC at 1GS/s 16 bits

- 4 channels of DAC at 2.8GS/s 16 bits

- XCKU060-2FFVA1517 (with XCKU085 or XCKU115 options)

- includes complete BSP capable of logging all 4 channels of ADC data to a PXIe host

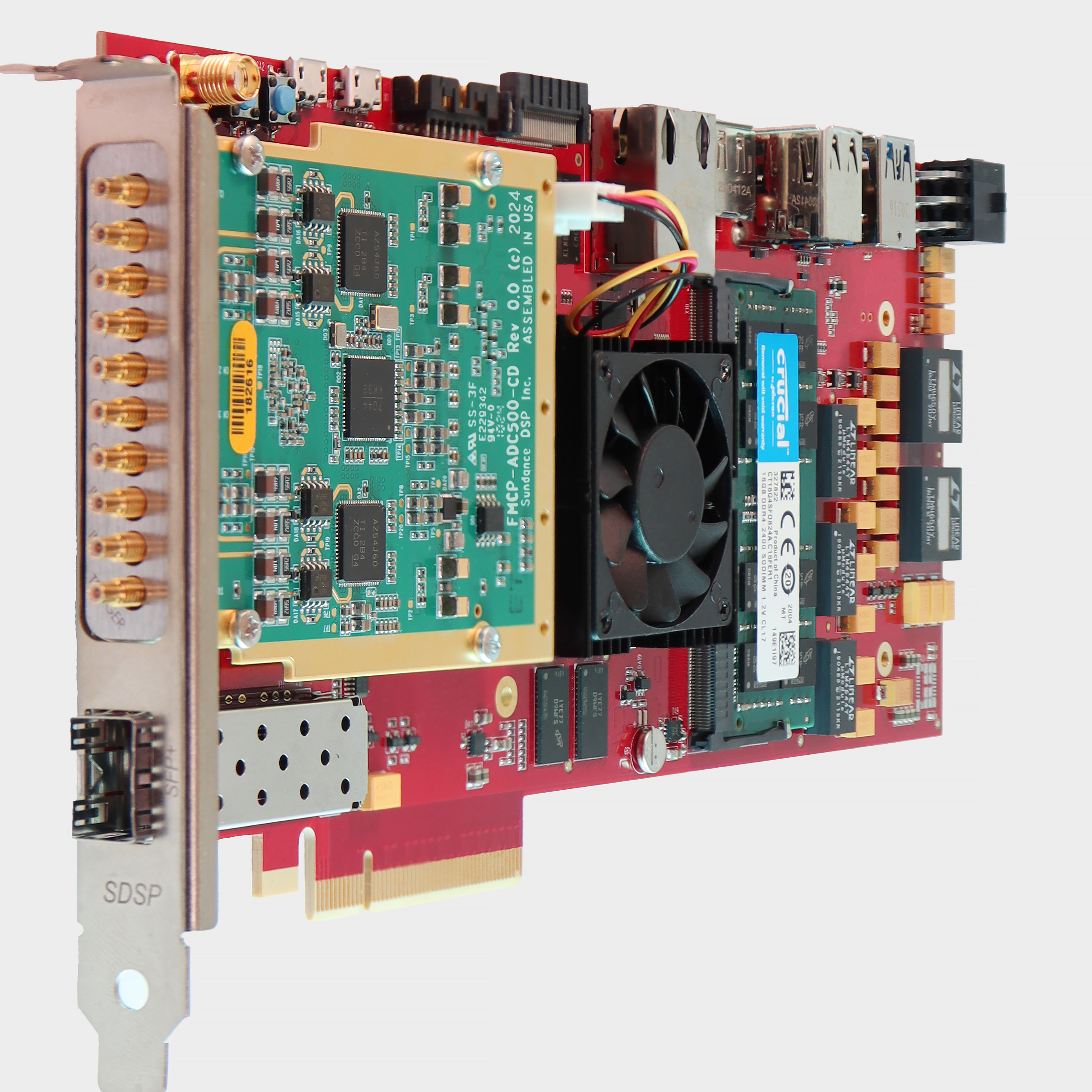

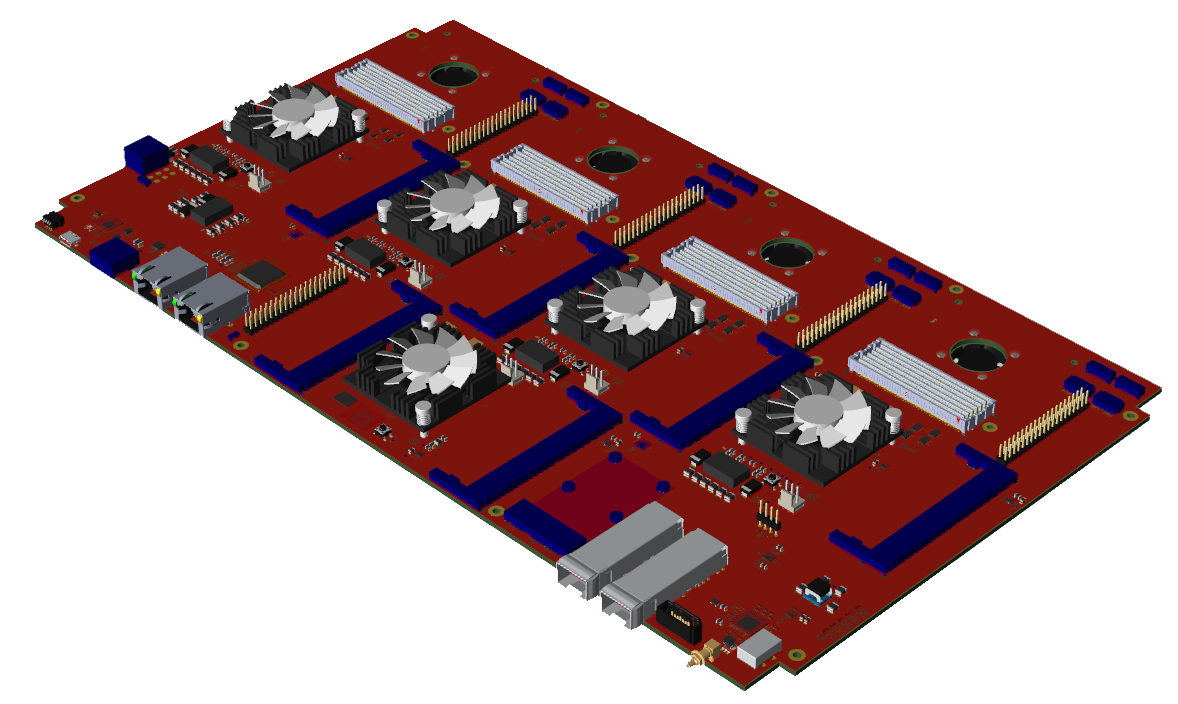

DL400 Data Logging Solution

DL400 is a high-speed, high-precision data acquisition and processing system designed for applications that demand real-time performance, large data throughput, and seamless integration. It is based on SE120 PCIe card and FMC-ADC500CD DAQ.

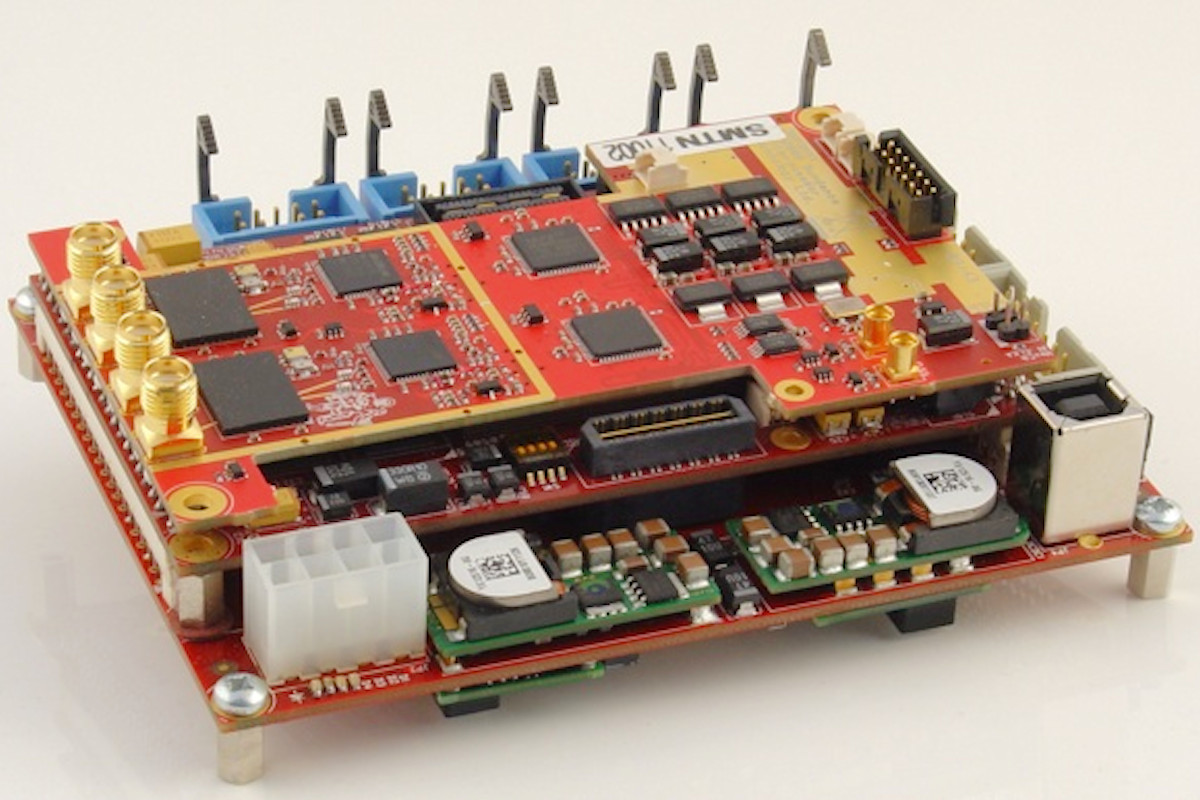

DSP8080-AIMM

- MIMO RF Tranceiver

- Dual 12-bit ADCs and dual 12-bit DACs

- Virtex-5 FXT FPGA (XC5VFX70T or XC5VFX100T)

- DDR2 SDRAM (1GByte per bank)

DSP8o2.11S

- IEEE802.11 a/b/g/- SISO and MIMO Development Platform

- Xilinx and Altera FPGAs (in Verilog/VHDL)

- FPGA control through 32 x 32 bit registers

Dual RF MIMO

Based on Xilinx Zynq UltraScale+ family. Depending on the choice of Zynq device (XCZU7EV / XCZU7EG/ XCZU11EG / XCZU7CG in C1156 package) it can be used for video decoding/encoding, digital communication or image processing and AR/VR applications.