Introduction

The FMC-RPi represents an innovative approach to FPGA development by bridging two of the most vibrant hardware ecosystems: FPGA platforms utilizing the VITA 57.1 FMC standard and the extensive Raspberry PI HAT and PMOD peripheral markets. Currently in the design phase, this HPC FMC module aims to dramatically accelerate prototyping and deployment of FPGA-based applications by leveraging thousands of off-the-shelf peripherals.

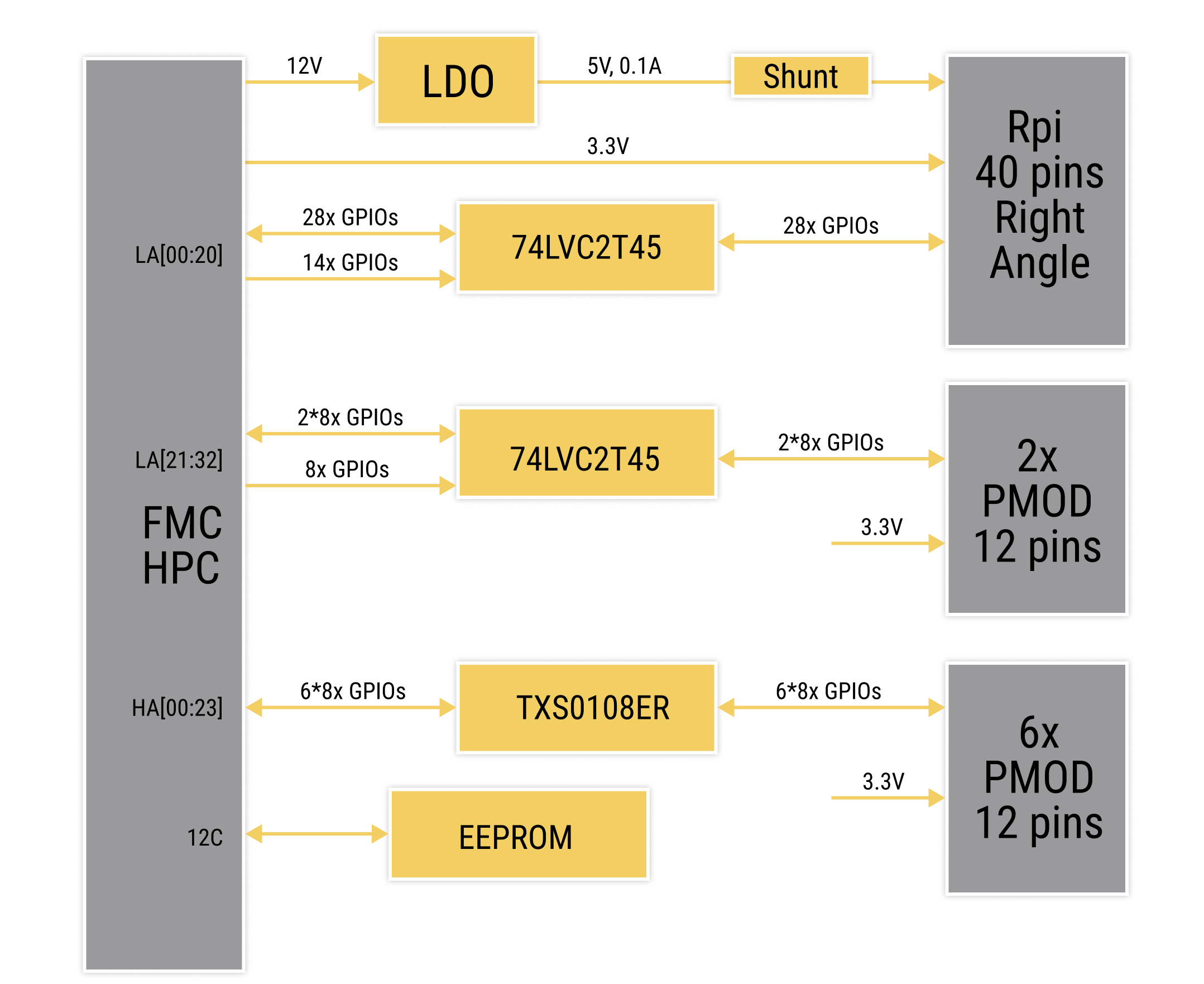

Architecture Overview

Core Design Philosophy

The FMC-RPi module operates as a bidirectional bridge, allowing FPGA carrier boards with FMC connectors to interface with Raspberry Pi 40-pin HATs and up to eight 12-pin PMOD modules. The module positions the FPGA as the master controller for both peripheral types, enabling sophisticated FPGA logic to directly command and coordinate a diverse array of commercial off-the-shelf hardware.

Form Factor and Compatibility

The module implements the VITA 57.1 High Pin Count (HPC) FMC standard, providing maximum connectivity and bandwidth. However, it maintains backward compatibility with Low Pin Count (LPC) FMC carriers, albeit with reduced functionality—specifically, the HA lane-connected PMOD connectors become unavailable on LPC carriers.

Technical Architecture Breakdown

1. Level Translation Subsystem

One of the most critical design challenges in bridging FPGA and peripheral ecosystems is voltage level translation. The FMC-RPi employs a dual-translator architecture:

74LVC2T45 Translators (RPi + 2 PMODs)

- Function as controllable bidirectional level shifters

- Support the Raspberry Pi header and two PMOD connectors

- Architecture: One direction (DIR) signal controls two GPIO lines

- Design consideration: This 2:1 DIR-to-GPIO ratio requires careful peripheral selection and planning. Peripherals using both controlled GPIOs must operate in the same direction simultaneously

TXS0108 Translators (6 PMODs)

- Handle the remaining six PMOD connectors on HA lanes

- Automatic direction sensing eliminates DIR pin complexity

- Critical specification: 4kΩ output impedance for static loads

- Load requirement: Total pull-down impedance must exceed 20kΩ

- Voltage floor: Minimum VADJ of 1.4V required for operation

- Throughput: Maximum data rates decrease with lower VADJ voltages

This dual-translator approach balances controllability for the RPi interface against the simplicity of automatic sensing for the majority of PMOD ports.

2. Power Distribution Network

The FMC-RPi implements a sophisticated power delivery system supporting multiple voltage domains:

Raspberry Pi Header Power

- 5V rail: 100mA capacity

- 3.3V rail: 1A capacity

- Design feature: Shunt resistor allows disconnection of 5V supply from RPi header for applications where external power is preferable or 5V rail protection is critical

PMOD Power

- 3.3V rail: 3A capacity across all eight PMOD connectors

- Substantial current capability enables power-hungry sensor arrays and communication modules

VADJ Support Range

- Nominal: 1.2V to 3.3V

- Practical floor: 1.4V when using HA lane PMODs (due to TXS0108 requirements)

- This voltage flexibility enables compatibility with modern low-voltage FPGA I/O banks

3. FMC Interface Standards

EEPROM Implementation

- HPC FMC module EEPROM for carrier board identification

- Stores FMC module metadata per VITA 57.1 specification

- Enables automatic resource allocation and pin mapping in carrier board BSPs

Use Cases and Applications

Industrial Automation

The FMC-RPi excels in industrial control scenarios where diverse sensor and actuator interfaces must be rapidly integrated:

- Sensor fusion platforms: Connect multiple PMOD sensor modules (temperature, pressure, proximity, optical) while using RPi HATs for industrial networking protocols (EtherCAT, PROFINET)

- Motor control: Deploy RPi motor driver HATs while leveraging FPGA for real-time control loops and safety interlocks

Artificial Intelligence and Edge Computing

The module enables heterogeneous AI architectures:

- Neural network acceleration: FPGA handles quantized inference while PMOD modules provide sensor interfaces and RPi HATs enable connectivity (4G/5G, WiFi)

- AI-enabled signal processing: Combine FPGA DSP capabilities with AI accelerator for adaptive filtering and pattern recognition

- Distributed intelligence: Deploy multiple FMC-RPi systems with consistent peripheral interfaces across edge nodes

Robotics

Robotics applications benefit from the module’s ability to consolidate diverse I/O requirements:

- Sensor integration: IMUs, LIDAR, ultrasonic, and optical sensors via PMOD interfaces

- Motor control: Stepper and servo drivers via RPi HATs with FPGA-based trajectory planning

- Communication: Multiple PMOD modules for CAN bus, RS-485, and other industrial protocols

- Real-time coordination: FPGA ensures deterministic timing for sensor fusion and control loops

Data Acquisition and Processing

High-speed data acquisition systems leverage the FMC’s bandwidth:

- Multi-channel ADC/DAC systems: Connect analog front-ends via PMOD modules

- Protocol conversion: Bridge legacy industrial protocols to modern networks

- Timestamping and logging: FPGA-based precision timestamping with storage via RPi HATs

AI-Enabled RF Signal Processing

The module’s design specifications align well with software-defined radio and RF applications:

- RF front-ends: Connect RF transceiver PMODs with FPGA-based digital signal processing

- AI modulation recognition: Combine RF signal acquisition with neural network classification

- Adaptive filtering: Machine learning algorithms adjust filter parameters in real-time

- Spectrum monitoring: Deploy multiple sensor heads with centralized FPGA processing

Design Considerations and Limitations

1. Level Translator Drive Capability

The TXS0108’s 4kΩ output impedance requires careful attention to peripheral input characteristics. When selecting PMOD modules for HA lanes:

- Verify input impedance specifications exceed 20kΩ

- Avoid peripherals with heavy capacitive loading

- Consider signal integrity for high-speed protocols

- Test drive strength adequacy during the prototyping phase

2. Direction Control Architecture

The 74LVC2T45’s shared DIR signal for paired GPIOs imposes a constraint:

- Peripherals on controlled pairs must not require simultaneous bidirectional operation on both GPIOs

- Most I2C, SPI, and UART implementations remain compatible

- Custom peripheral selection may require pin assignment planning

- Document your GPIO direction requirements early in the design phase

3. VADJ Voltage Selection

The VADJ voltage selection involves multiple tradeoffs:

- Values below 1.4V disable HA lane PMODs

- Lower VADJ reduces TXS0108 throughput

- VADJ must match FPGA I/O bank capabilities

- Consider the thermal implications of I/O standard selection

4. LPC vs HPC Carrier Compatibility

When using LPC FMC carriers:

- Six HA lane PMOD connectors become unavailable

- Only the RPi header and two 74LVC2T45-controlled PMODs remain functional

- Evaluate whether reduced peripheral count meets application requirements

- HPC carriers unlock full module capability

Board Support Package and Integration

A complete BSP with Linux drivers for the SE120 Xilinx Zynq UltraScale+ MPSoC PCIe card will be provided. This BSP is expected to include:

- Device tree overlays for FMC-RPi detection and configuration

- Kernel drivers for level translator control

- User-space libraries for GPIO access

- Example applications demonstrating common peripheral types

- Documentation for custom peripheral integration

The SE120 integration provides a reference implementation that can be adapted to other Zynq UltraScale+ and general FPGA platforms with FMC connectivity.

Rapid Prototyping Advantages

The FMC-RPi’s primary value proposition lies in dramatically reduced development time:

Traditional FPGA Peripheral Development:

- Design a custom carrier board or mezzanine

- Route high-speed signals and power distribution

- Source and solder components

- Debug hardware issues

- Develop drivers and firmware

- Iterate through multiple board spins

FMC-RPi Approach:

- Select appropriate off-the-shelf HATs and PMODs

- Plug into FMC-RPi module

- Configure level translators

- Begin application development with proven hardware

This approach can compress months-long hardware development cycles into days or weeks, particularly valuable for proof-of-concept work, research projects, and low-volume specialized applications.

Ecosystem Access

Raspberry Pi HAT Ecosystem: Thousands of commercially available HATs covering communications (LoRa, cellular, WiFi), displays, motor drivers, relay boards, audio interfaces, GPS modules, and specialized sensors. The maturity and breadth of this ecosystem provides immediate access to industrial-grade peripherals with proven software support.

PMOD Module Ecosystem: The Digilent PMOD standard has spawned hundreds of compatible modules from multiple vendors. Categories include analog I/O, digital I/O, communication interfaces, sensors, displays, and specialized functions like cryptographic accelerators. The 12-pin interface standardization ensures mechanical and electrical compatibility across vendors.

Target Development Scenarios

The FMC-RPi shines in several specific scenarios:

- Research and education: Universities and research labs can rapidly assemble custom measurement and control systems

- Product concept validation: Companies can test market viability before committing to custom hardware

- Low-volume production: Applications requiring 10-1000 units may find the FMC-RPi approach more economical than custom designs

- Modular test equipment: Build flexible test systems with swappable measurement capabilities

- Emergency engineering: When project timelines compress, off-the-shelf peripherals eliminate procurement and fabrication delays

Invitation to Early Adopters

The FMC-RPi is currently in the design phase, representing an ideal opportunity for potential users to influence the final product. We’re actively seeking feedback from the technical community in several areas:

Feature Requests: If your application would benefit from modifications or additions to the current design, now is the time to make your voice heard. Possibilities include:

- Additional PMOD connectors

- Alternative level translator configurations

- Enhanced power delivery capabilities

- Specialized signal conditioning

- Different FMC form factors (LPC native design)

- Specific protocol support (CAN, RS-485, etc.)

Availability Inquiries Organizations interested in evaluation units, development partnerships, or volume pricing should contact us to discuss timelines and requirements. Early adopters may receive preferential access to initial production runs and BSP development resources.

Beta Testing Program We’re assembling a beta testing cohort to validate the design across diverse application domains. Beta participants will receive:

- Pre-production hardware

- Direct engineering support

- Early access to BSP and documentation

- Influence over final design refinements

Contact Information: Please reach out through the Sundance DSP website to express interest, request additional technical information, or submit feature suggestions. Your input during the design phase ensures the FMC-RPi meets real-world requirements across the broadest possible range of applications.